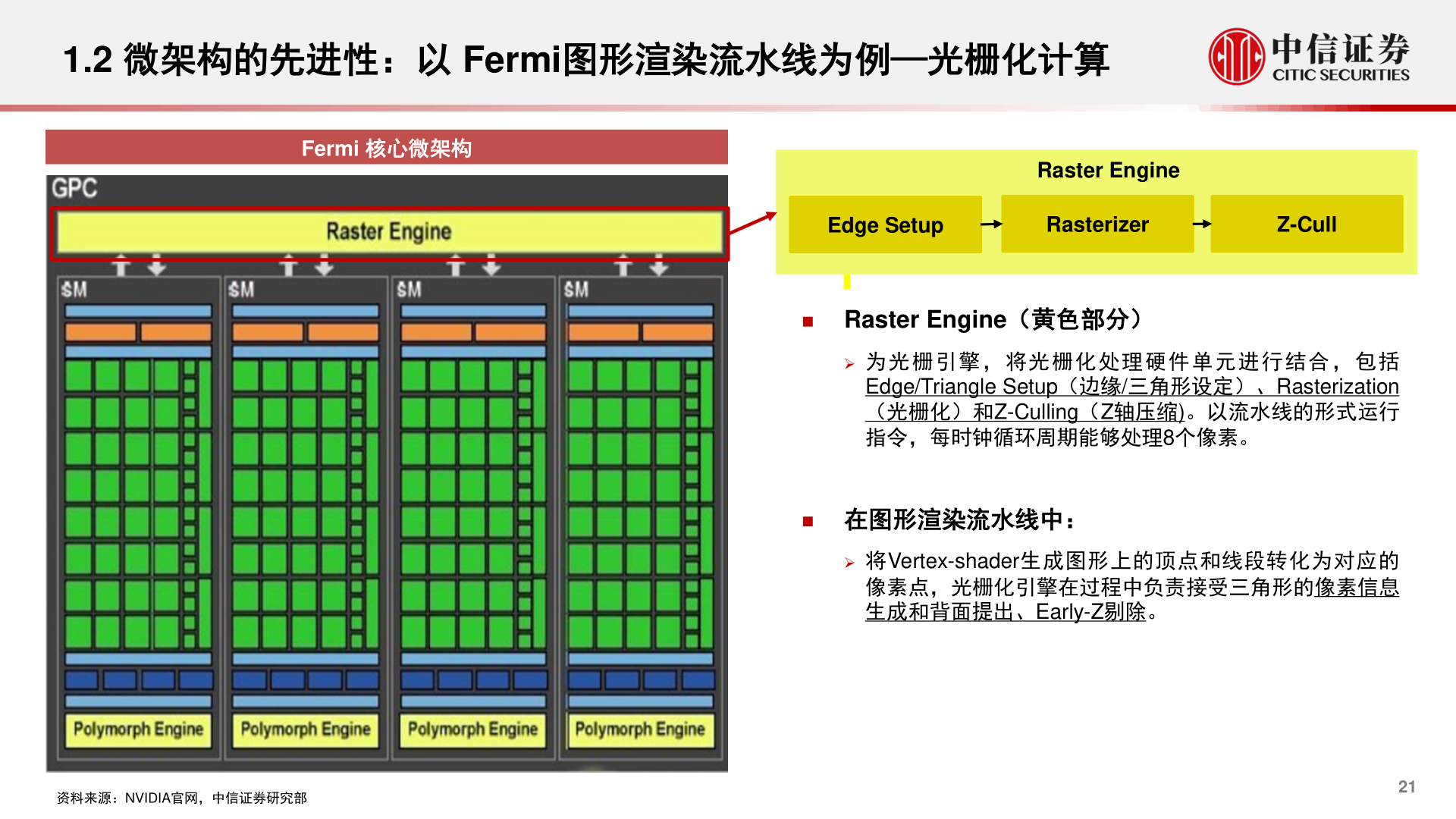

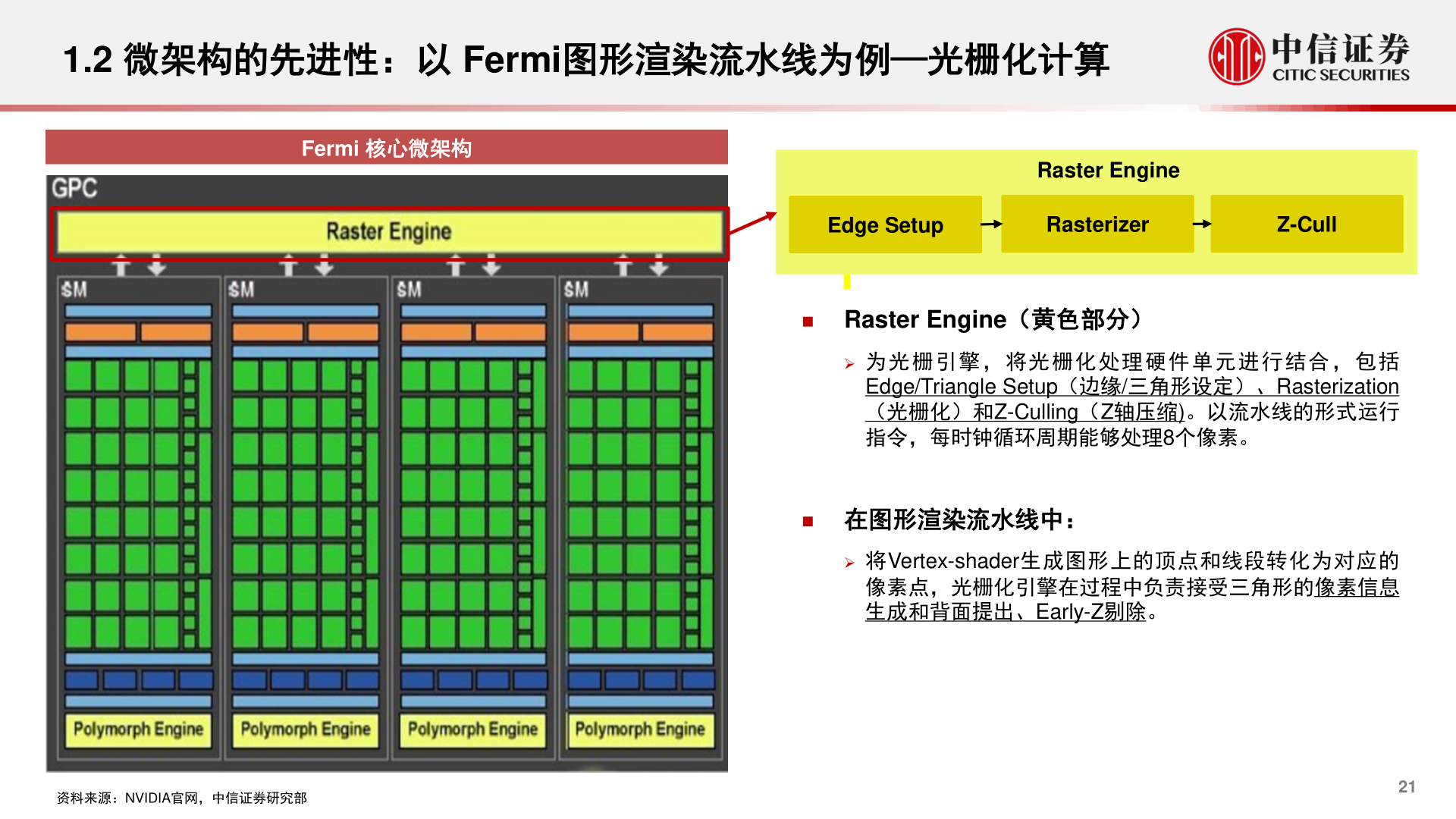

> 数据图表如何解释1.2 微架构的先进性:以 Fermi图形渲染流水线为例—光栅化计算

2023-2-01.2 微架构的先进性:以 Fermi图形渲染流水线为例—光栅化计算Fermi 核心微架构Raster EngineEdge SetupRasterizerZ-Cull Raster Engine(黄色部分) 为光 栅 引擎,将光栅化 处理硬件单元进 行结合 ,包括Edge/Triangle Setup(边缘/三角形设定)、Rasterization(光栅化)和Z-Culling(Z轴压缩)。以流水线的形式运行指令,每时钟循环周期能够处理8个像素。 在图形渲染流水线中: 将Vertex-shader生成图形上的顶点和线段转化为对应的像素点,光栅化引擎在过程中负责接受三角形的像素信息生成和背面提出、Early-Z剔除。资料来源:NVIDIA官网,中信证券研究部21