> 数据图表一起讨论下P24

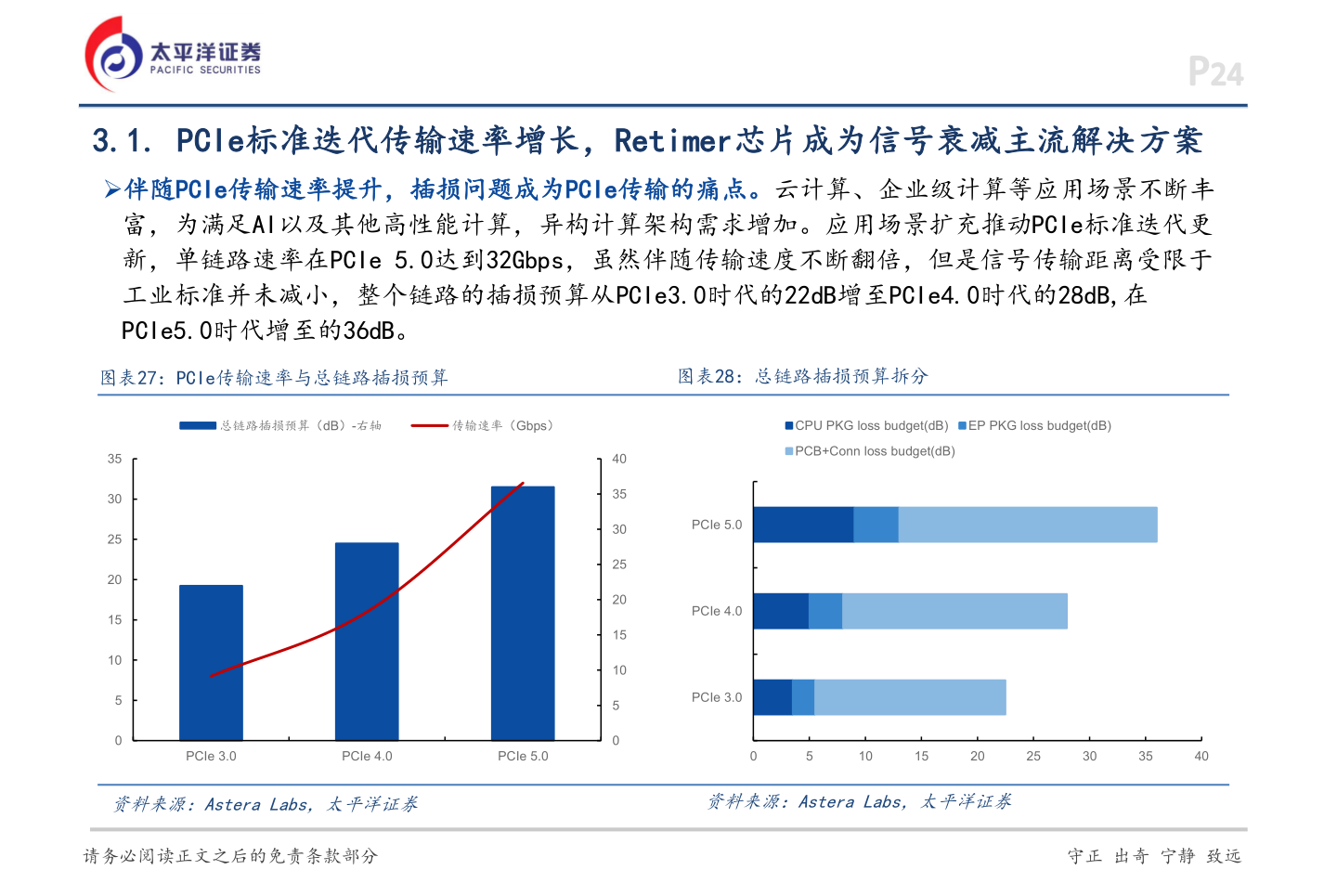

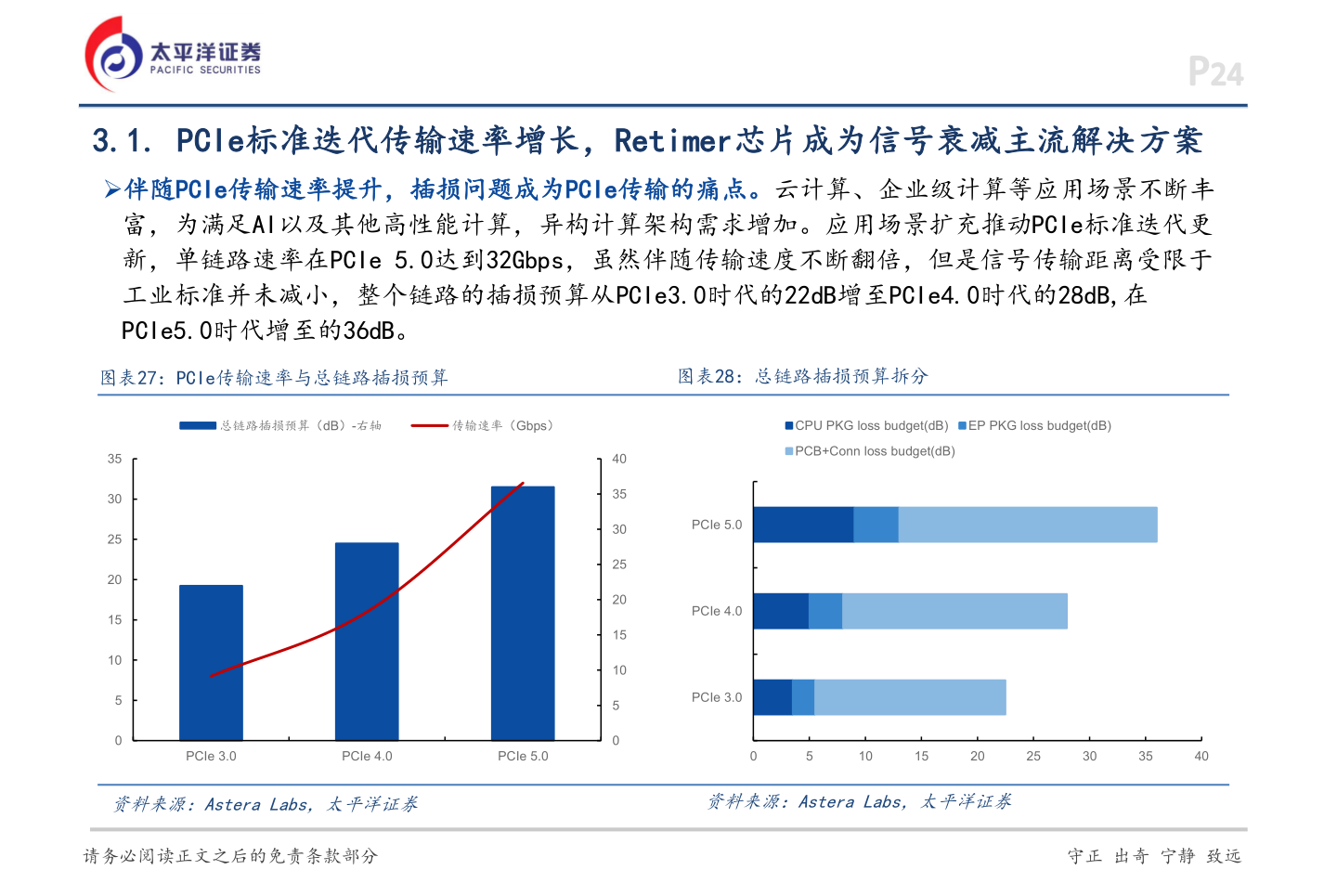

2025-9-1P243.1. PCIe标准迭代传输速率增长,Retimer芯片成为信号衰减主流解决方案➢伴随PCIe传输速率提升,插损问题成为PCIe传输的痛点。云计算、企业级计算等应用场景不断丰富,为满足AI以及其他高性能计算,异构计算架构需求增加。应用场景扩充推动PCIe标准迭代更新,单链路速率在PCIe 5.0达到32Gbps,虽然伴随传输速度不断翻倍,但是信号传输距离受限于工业标准并未减小,整个链路的插损预算从PCIe3.0时代的22dB增至PCIe4.0时代的28dB,在PCIe5.0时代增至的36dB。图表27:PCIe传输速率与总链路插损预算图表28:总链路插损预算拆分总链路插损预算(dB)-右轴传输速率(Gbps)CPU PKG loss budget(dB)EP PKG loss budget(dB)35302520151050PCB+Conn loss budget(dB)4035302520151050PCIe 5.0PCIe 4.0PCIe 3.0PCIe 3.0PCIe 4.0PCIe 5.00510152025303540资料来源:Astera Labs,太平洋证券资料来源:Astera Labs,太平洋证券请务必阅读正文之后的免责条款部分守正 出奇 宁静 致远