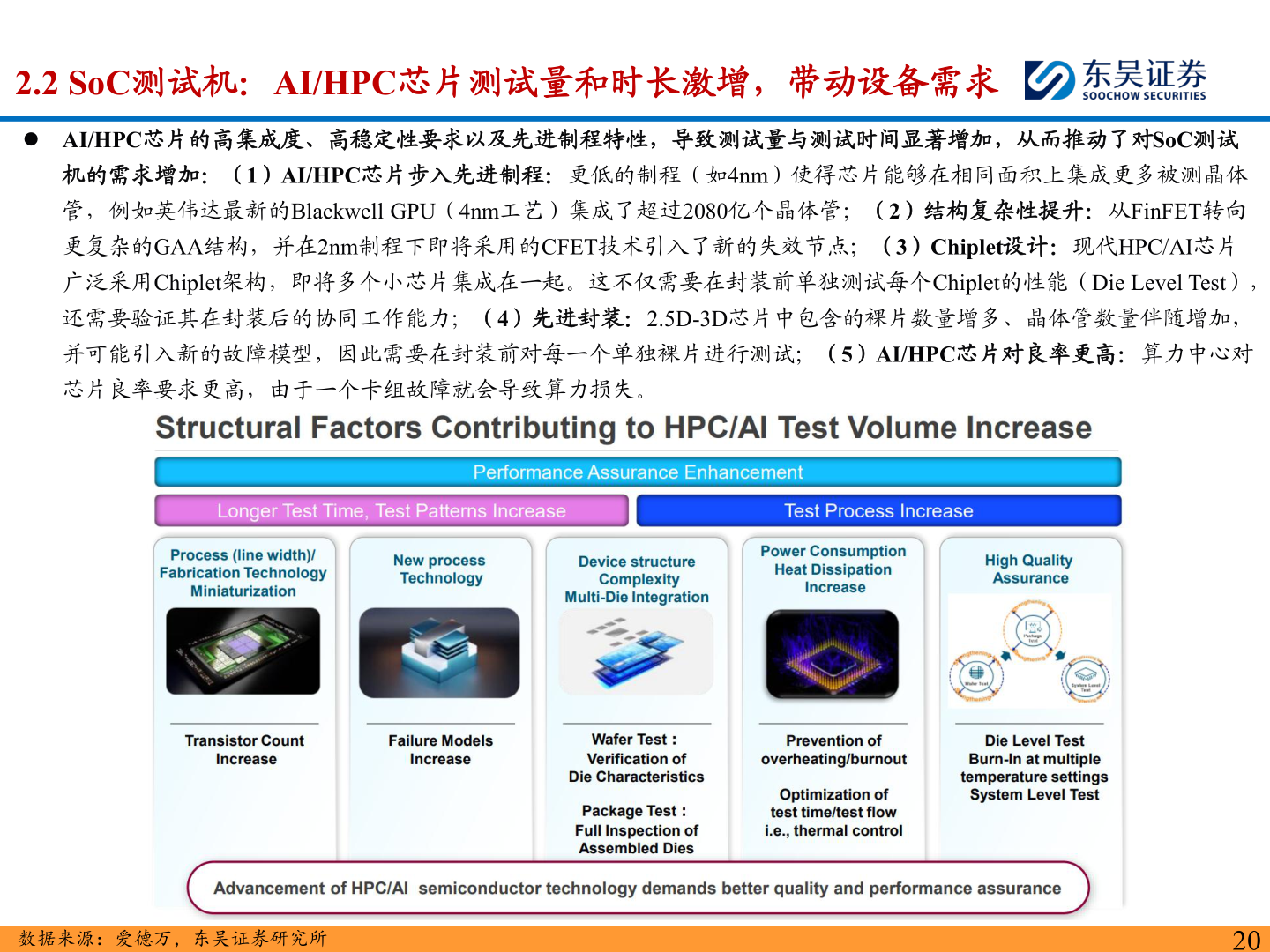

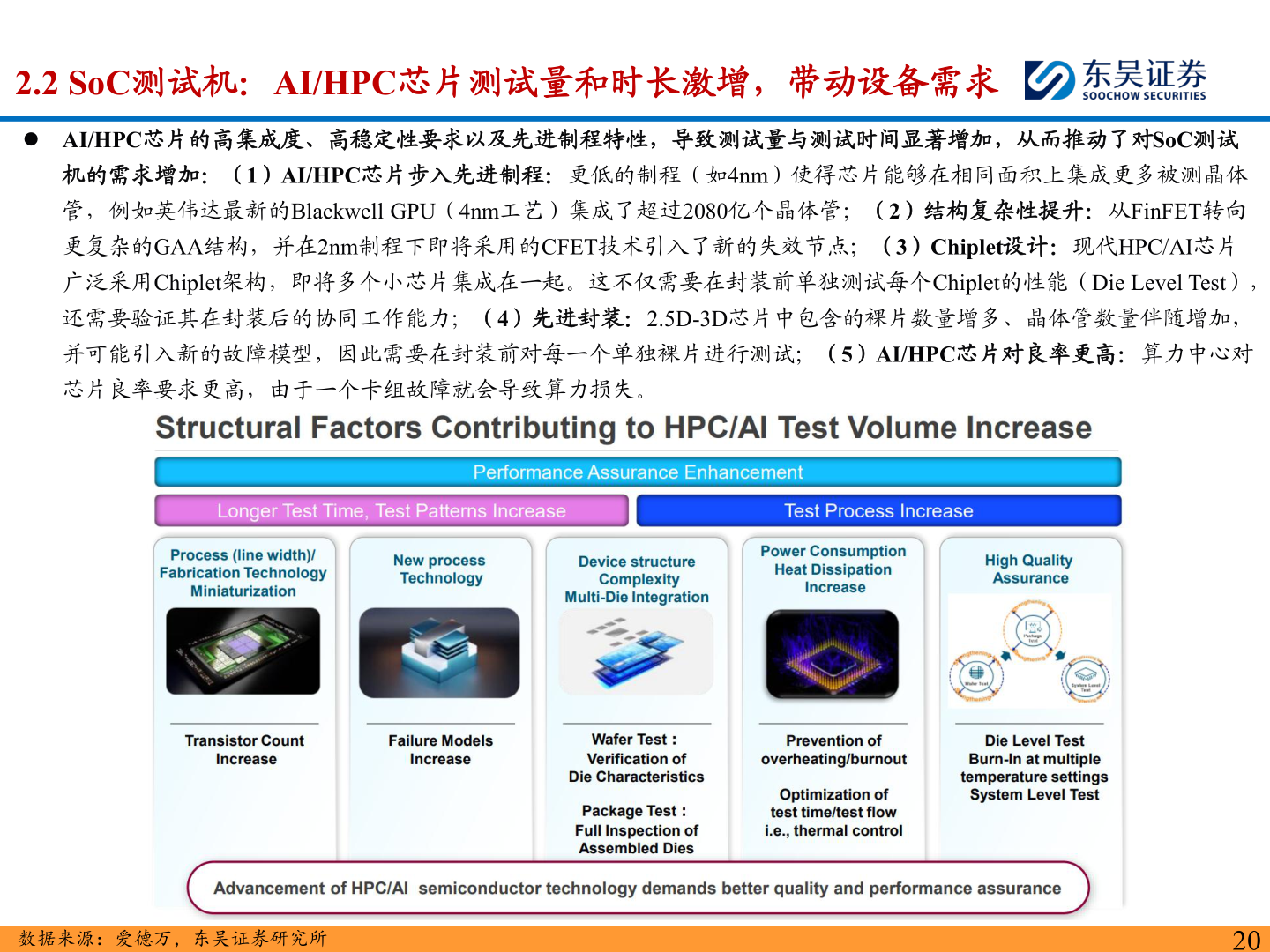

> 数据图表想问下各位网友2.2 SoC测试机:AI/HPC芯片测试量和时长激增,带动设备需求

2025-9-02.2 SoC测试机:AI/HPC芯片测试量和时长激增,带动设备需求⚫ AI/HPC芯片的高集成度、高稳定性要求以及先进制程特性,导致测试量与测试时间显著增加,从而推动了对SoC测试机的需求增加:(1)AI/HPC芯片步入先进制程:更低的制程(如4nm)使得芯片能够在相同面积上集成更多被测晶体管,例如英伟达最新的Blackwell GPU(4nm工艺)集成了超过2080亿个晶体管;(2)结构复杂性提升:从FinFET转向更复杂的GAA结构,并在2nm制程下即将采用的CFET技术引入了新的失效节点;(3)Chiplet设计:现代HPC/AI芯片广泛采用Chiplet架构,即将多个小芯片集成在一起。这不仅需要在封装前单独测试每个Chiplet的性能(Die Level Test),还需要验证其在封装后的协同工作能力;(4)先进封装:2.5D-3D芯片中包含的裸片数量增多、晶体管数量伴随增加,并可能引入新的故障模型,因此需要在封装前对每一个单独裸片进行测试;(5)AI/HPC芯片对良率更高:算力中心对芯片良率要求更高,由于一个卡组故障就会导致算力损失。数据来源:爱德万,东吴证券研究所20